### glasses for microphotonics

International Workshop on Scientific Challenges for New Functionality in Glass

Washington DC Apr. 16, 2007

Ray DeCorby Associate Professor, ECE Department TRLabs Scientist University of Alberta Edmonton, Alberta, Canada

Collaborator Acknowledgements: Profs. Al Meldrum, Ying Tsui, Jim McMullin, Safa Kasap (U of Saskatchewan) Student Acknowledgements: Nakeeran Ponnampalam, Mahesh Pai, Trevor Allen, Tom Clement, Florian Lenz

### Outline

- <u>Microphotonics</u>: photonics on/with (silicon) electronics

- ⇒ microphotonic devices (photonic crystals, microcavities, etc.)

- $\Rightarrow$  motivation and drivers

- ⇒ back-end versus front-end integration of photonics

- **2** Glasses as enablers of microphotonics

- $\Rightarrow$  the glass transition as enabler

- $\Rightarrow$  metastability as enabler

- $\Rightarrow$  glasses as hosts: composite materials, etc.

- **B** Scientific challenges for glasses in microphotonics

- $\Rightarrow$  high index contrast devices

- $\Rightarrow$  compatible processing: thermal 'window', etc. ...

### **Microphotonics**

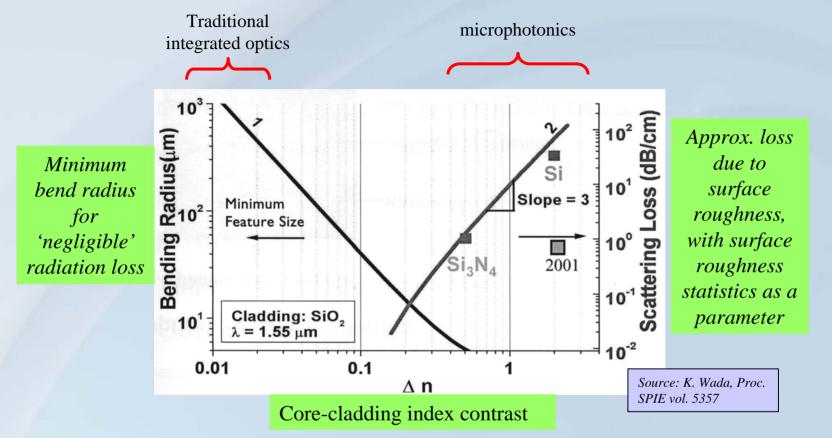

<u>microphotonics (1)</u>: technologies for realization of chip-scale (μm to mm) photonic devices

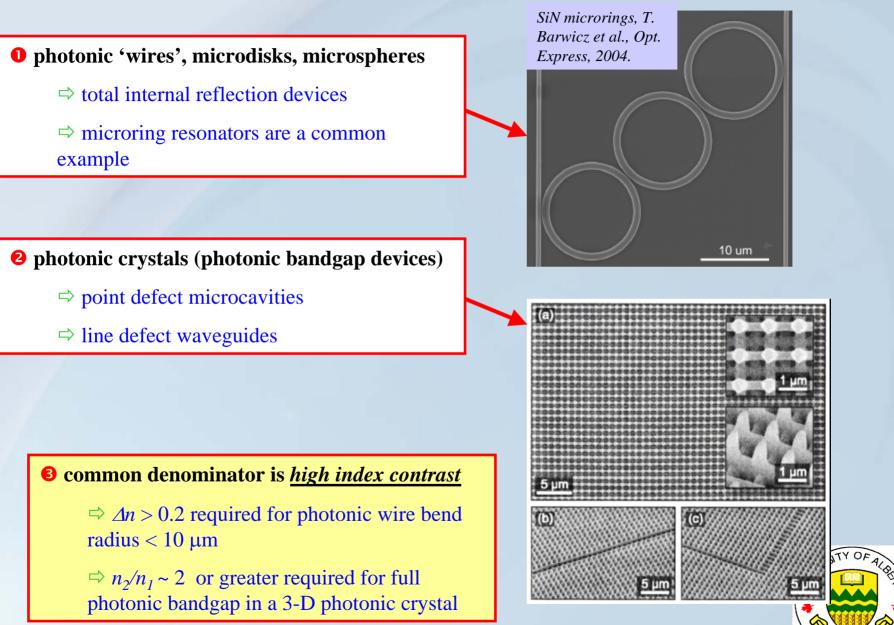

⇒ photonic crystal and wire waveguides and microcavities that enable light to be bent and confined on micron scales, without excessive light radiation

⇒relies on high refractive index contrast between compatible materials

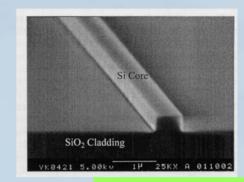

Silicon (on insulator) photonic wire waveguides

2 microphotonics (2): fabrication of photonic/optical devices using the same processing steps employed in microelectronics

$\Rightarrow$  this definition is a bit more restrictive, implies CMOS compatible materials and process flow, etc.

### **Microphotonics – building blocks**

### Glasses as microphotonics materials (1)

"Glass ...(accounts) for more than 90 percent of all optical elements manufactured" – W.J. Tropf et al. in *OSA Handbook of Optics, Vol. II*

Many traditional advantages of glass transfer well to the microphotonics regime:

#### **1** <u>cheap, isotropic, homogeneous:</u>

- $\Rightarrow$  ease of forming high quality films, etc.

- ⇒ low volume scattering (no grain boundaries)

- $\Rightarrow$  no 'preferred' directions (ie. on chip)

#### **2** processing enabled by glass transition:

$\Rightarrow$  structures can be formed (molded, drawn, etc.) by heating above glass transition, then freezing in place

$\Rightarrow$  flow and reflow can produce nm-scale surface roughness

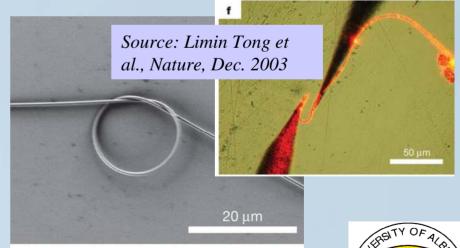

Source: Limin Tong et al., Nature, Dec. 2003

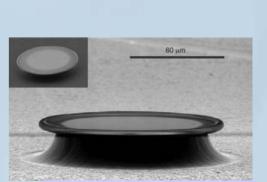

Source: D.K. Armani et al., Nature, Feb. 2003

### Glasses as microphotonics materials (2)

Many traditional advantages of glass transfer well to the microphotonics regime:

#### **B** <u>metastibility as an enabler:</u>

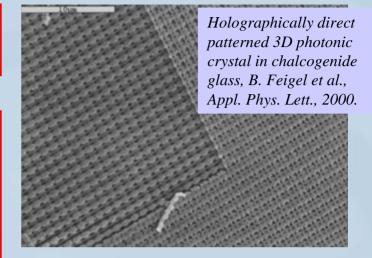

⇒ energetic beams (light, e-beams, ion beams) of modest intensity can often induce transitions between 'metastable states'

⇒ can be exploited for direct patterning of microdevices, and post-fabrication *trimming* of microphotonic devices

#### **4** functionality by 'doping' (glasses as hosts):

$\Rightarrow$  rare-earth ions, quantum dots, metal nanoclusters can be incorporated for light emission, nonlinear, magnetooptic effects, etc.

$\Rightarrow$  the glass host lends its other advantages (ease of processing, etc.)

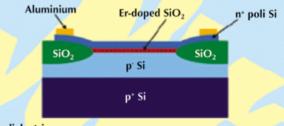

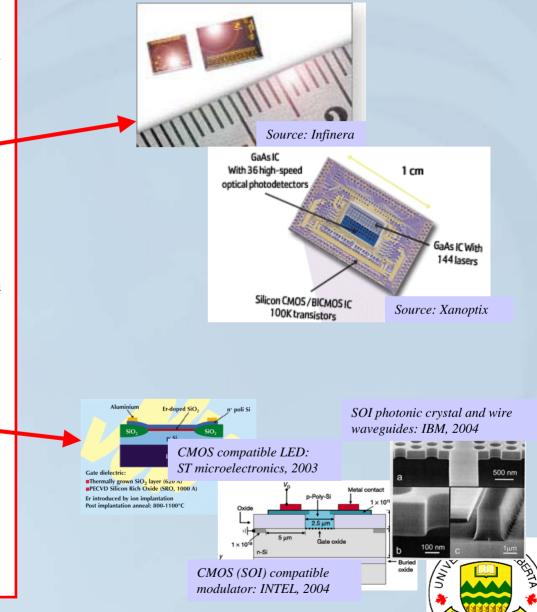

Gate dielectric:

Thermally grown SiO<sub>2</sub> layer (620 A) PECVD Silicon Rich Oxide (SRO, 1000 A)

Er introduced by ion implantation Post implantation anneal: 800-1

CMOS compatible LED: ST microelectronics, 2003

aside: amorphous materials (ie.  $SiO_2$  gate dielectrics, etc.) continue to be of great importance to microelectronics

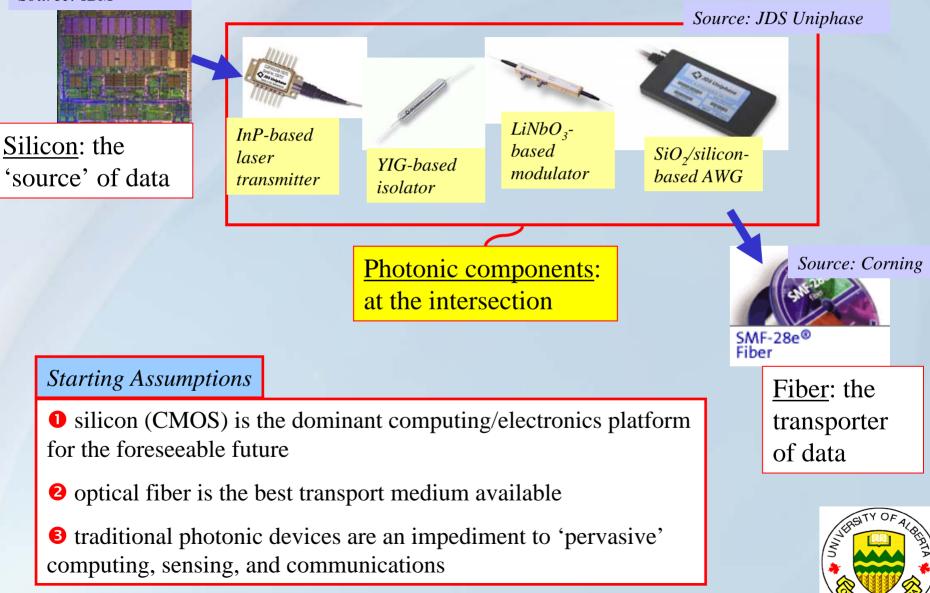

### The silicon-photonics intersection

Microprocessor chip Source: IBM

### The need for microphotonics in fiber networks (1)

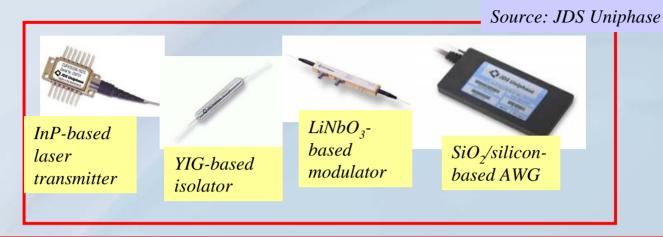

• traditional photonics: <u>high-tech components</u>, 'arcane and expensive' <u>systems</u>.

- ⇒ different (specialized) material systems for every optical function

- ⇒ devices are 'integrated', but negligible system integration

- ⇒ devices typically interconnected by fiber pigtails

- **2** current approach leads to <u>poor economics</u>

- $\Rightarrow$  each photonic device is expensive (several k to several 10s of k)

$\Rightarrow$  optical alignment (of each device to its fiber pigtails) is critical and challenging; packaging accounts for ~50-90% of the cost of a device ...

### The need for microphotonics in fiber networks (2)

• the economics of optical networks needs fundamental change

⇒ the current approach (no system integration) is economic (barely) for longhaul high-capacity systems

$\Rightarrow$  does not work as effectively in the sectors with high growth potential: fiber-to-the-home, pons, metro, etc.

**2** <u>integration needed</u>: of diverse photonic devices, between optics/electronics

$\Rightarrow$  traditional integrated approaches (InP, LiNbO<sub>3</sub>...) advancing but yet to break through (cost, yield, etc. remain issues)

$\Rightarrow$  need a single standard platform for optical integration (*silicon*?); glasses can play a role here (flexibility in processing, composition, etc. )

"...optical networks are arcane and expensive ... The goal of bringing optical networking down to the curb and ultimately to the PC can only be met if high-performance, low-cost, low-power optical components are available." M. Paniccia, Director of Photonics Research, Intel

IMI Werkshop on Scientific Chancenges for the Panenonality in Grass, reashington DC, Apr. 16, 2007, Ray DeCorby

#### *Electronics & photonics – perfect marriage?*

• they need each other

$\Rightarrow$  photonic networks need closer integration with silicon electronics (see above)

$\Rightarrow$  silicon electronics will increasingly need photonics for high speed interconnects (board to board, chip to chip, intrachip?)

**2** *microphotonics* might be a much needed boost for photonics:

> $\Rightarrow$  recovery from the fiber boom/bust cycle has been slow

Source: N. Savage, "Linking with Light", IEEE Spectrum, Aug. 2002.

#### wireless

**internet**

15+ Years Experts disagree on whether connects will ever conn

□ biotech

- □ ICs

- nanotech

- infotech

- robots

- other

optics/photonics

Answers to "most important technology for the coming decade" IEEE Spectrum, Nov. 2004

IMI Workshop on Scientific Challenges for New Functionality in Glass, wasnington DC, Apr. 10, 2007, Kay DeCorby

2-5 Years

5-10 Years

Optical communications will enter the computer, connecti one circuit board to another.

#### Silicon-Photonics Convergence in Industry

#### **1** Optical networking industry

⇒ hybrid integration between optical components and silicon CMOS increasing in sophistication...)

⇒ CMOS plays an increasingly important role in fiber networks (forward error correction, advanced line coding functions, O/E/O ...)

⇒ is hybrid III-V / CMOS integration approach truly scalable in a mass-market sense?

#### **2** Silicon IC industry

⇒ the big silicon firms have increased their investment in photonics

⇒will a *truly integrated optoelectronics technology* be incubated by the IC industry, with optical networks as one of the main beneficiaries?

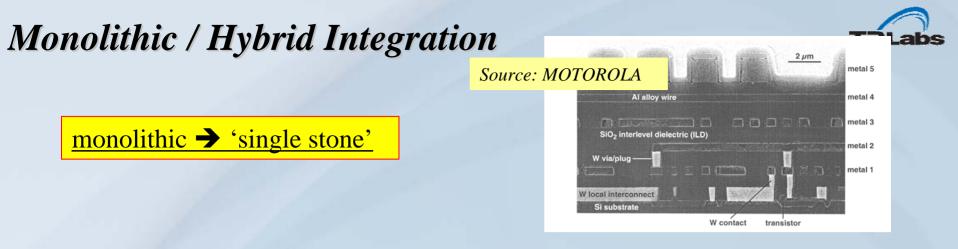

• Strictly speaking, even a silicon IC is not a monolithic system

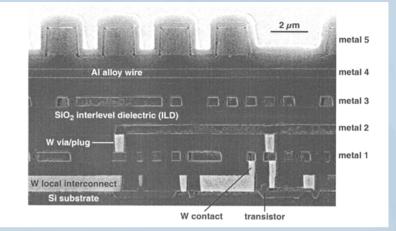

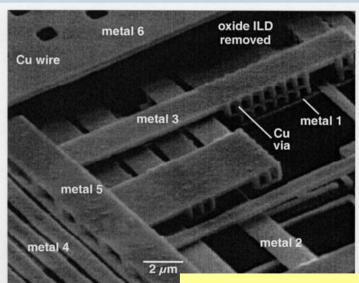

$\Rightarrow$  relies on a diverse set of mutually compatible materials (silicon, polySi, SiO<sub>2</sub>, Al, Cu, W ...)

$\Rightarrow$  sometimes monolithic is equated with processes restricted to the 'standard' set of materials

Same flexibility should be afforded to *photonic* integration as electronic integration; possible (?) <u>working definitions</u> are:

① **Monolithic integration**: system fabricated on a single wafer using <u>automated mask</u> <u>alignment</u> and a defined set of process steps (thin film dep, lithography, implantation, diffusion, etching)

② **Hybrid integration:** system assembled by interconnecting separately fabricated parts, using techniques (pick and place, flip-chip, etc.) other than automated mask alignment

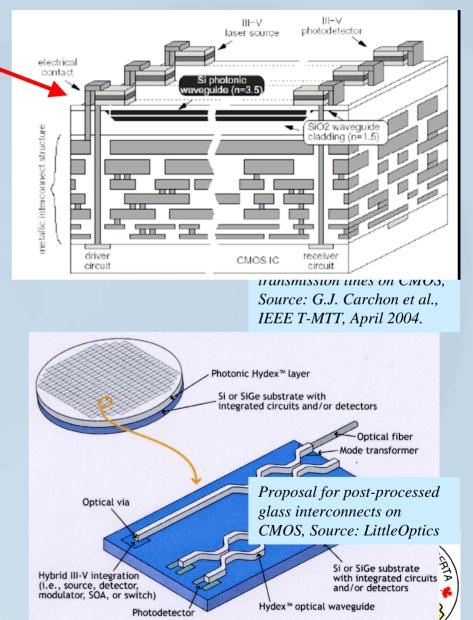

### Approaches to photonics on silicon (1)

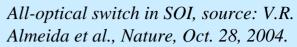

#### **1** front-end approach (especially SOI):

- ⇒ high-temperature processes OK

- ⇒ inherently compatible, but disruptive to the standard process flow

- ⇒ Photonics/electronics compete for real estate

- ⇒ restricted in terms of materials /functionality

- ⇒ range of photonic functions are possible using crystalline silicon

3-d photonic structures in SOI, source: P. Koonath et al., Appl. Phys. Lett., Aug. 2004.

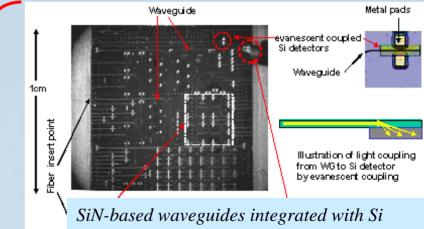

⇒ processing temperature somewhat variable, depending on exact placement in the process flow

$\Rightarrow$  more flexible than front-end approach

detectors on CMOS, source: M.J. Kobrinsky et al., Intel Tech. J., May 2004.

### Approaches to photonics on silicon (2)

back-end post-processing approach (above IC approach):

⇒analogous to above IC approach used for integration of RF devices on CMOS

#### i. potential advantages

⇒ least disruptive to the standard CMOS process flow

$\Rightarrow$  wide range of functional materials can be employed, in theory at least

⇒Possibility for 3-d integration, within a set of photonic interconnect levels

#### ii. overriding challenges

⇒ restricted processing temperatures (<400 C for 1-2 hours?), CTE issues

⇒ new materials/devices must be compatible with packaging-related temperature excursions and in-use IC temperatures (>100 C)

⇒ 'vias' required to link front-end optoelectronic devices (photodetectors, etc.) to back-end photonics

### Surface roughness in microphotonics (1)

• Surface (interface) scattering loss is a major challenge in microphotonics

⇒ chip-scale waveguides must be very small and have high core-cladding refractive index contrast

⇒ The Tien model for estimating scattering loss in a (slab) waveguide tells us:

$\alpha_s \sim \sigma^2 \Delta n^2$

$\alpha_{s}$  – scattering loss coefficient  $\sigma$  – standard deviation (characteristic amplitude) of the roughness  $\Delta n^{2} = n_{core}^{2} - n_{cladding}^{2}$

**2** scattering loss can be severe as  $\Delta n$  increases and core dimensions shrink  $(\alpha_S \sim 1/d^4)$

$\Rightarrow$  to minimize scattering loss, more accurate models (such as Payne-Lacey model) indicate that both the characteristic amplitude ( $\sigma$ ) and the <u>correlation length</u> ( $L_C$ ) of the roughness statistics must be low

SOI photonic wire, Sakai et al., Yokohama U.

### Surface roughness in microphotonics (2)

**1** light can be bent or confined on a µm scale, using either TIR or photonic crystal dielectric structures. Either approach requires:

- $\Rightarrow \Delta n \sim 1$  or greater

- $\Rightarrow$  precise feature definition on a sub-µm scale

- ⇒ nearly atomic level feature smoothness to minimize light scattering

#### Surface roughness in microphotonics (3)

$Q_{SS} = \frac{\lambda^2 D}{2\pi^2 \sigma^2 L_C}$   $D - microsphere \ diameter$

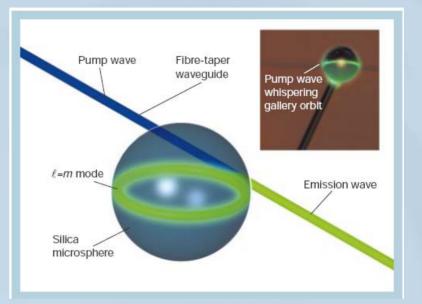

#### **1** Q-factor of a microsphere cavity often limited by surface scattering

$\Rightarrow Q \sim 10^{10}$  has been demonstrated for reflowed SiO<sub>2</sub> spheres formed at the end of glass fibers (the highest Q for any solid-state microcavity)

## $T_g$ -enabled fabrication of microphotonic structures

#### • liquids have optical quality surfaces through 'self-assembly'

⇒ glass devices can be formed from a liquid state, thus can benefit from the same surface-tension mediated assembly of smooth surfaces

Water droplet on a superhydrophobic surface, Source: C. Sanchez et al., J. Mater. Chem., vol. 15, 2005.

~50 µm microball lens by reflow of organic glass, Source: C.-T. Pan et al., Appl. Opt., vol. 43, 2004.

**2** roughness of a melt-formed or reflowed glass is determined by surface capillary waves (small amplitude fluctuations at a liquid surface, frozen into place at  $T_g$ )

$\Rightarrow$  SiO<sub>2</sub> surfaces have predicted rms roughness ~0.1 nm, confirmed many times

#### Photonic wires in crystals vs. glasses

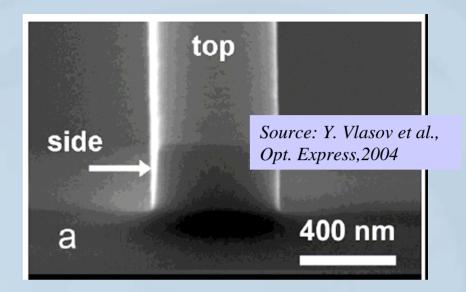

• ex. SOI photonic wires formed by stateof-the-art ebeam litho and dry etching

⇒ sidewall roughness as good as  $\sigma$ ~5 nm,  $L_c$ ~50 nm, with tight process control

$\Rightarrow$  propogation losses typically 3-10 dB/cm at  $\lambda$ =1550 nm

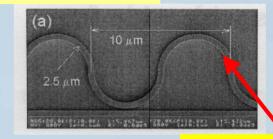

# **2** ex. SiO<sub>2</sub> wires fabricated by straightforward flame drawing technique

⇒ surface roughness as good as  $\sigma$ ~0.5 nm,  $L_C$ ~50 nm, with tight process control

$\Rightarrow$  propogation loss <1 dB/cm at  $\lambda$ =633 nm

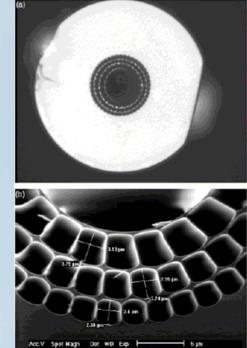

#### Photonic crystals – crystals vs. glasses

# • ex. line defect waveguides in 2-D SOI photonic crystals

$\Rightarrow$  ebeam litho and etching

⇒ best propagation losses typically 10 30 dB/cm, limited by roughness/disorder

a <u>500 nm</u>

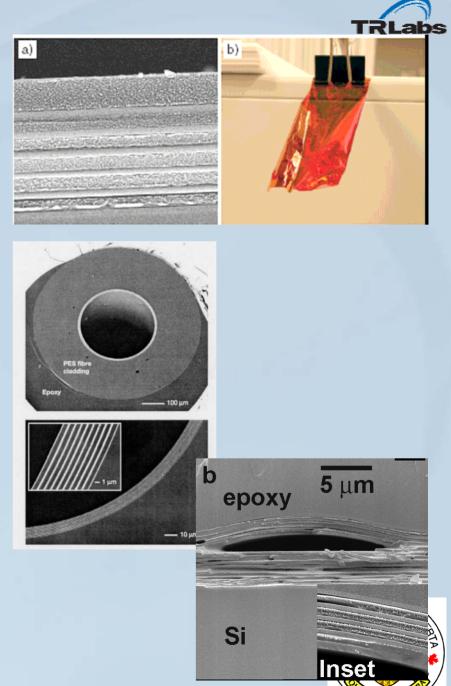

**2** ex. air-core waveguides in 2-D glass photonic crystals (ie. photonic crystal fibers)

$\Rightarrow$  rod and stack preform, fiber drawing

⇒ best propagation losses ~1 dB/km, limited by surface roughness of ~0.1 nm (see Roberts et al., *Opt. Express*, vol. 13, pp. 236-244 (2004).

> Can these benefits (surface tension mediated surfaces and order) be transferred to 2-D and 3-D photonic crystals on chips?

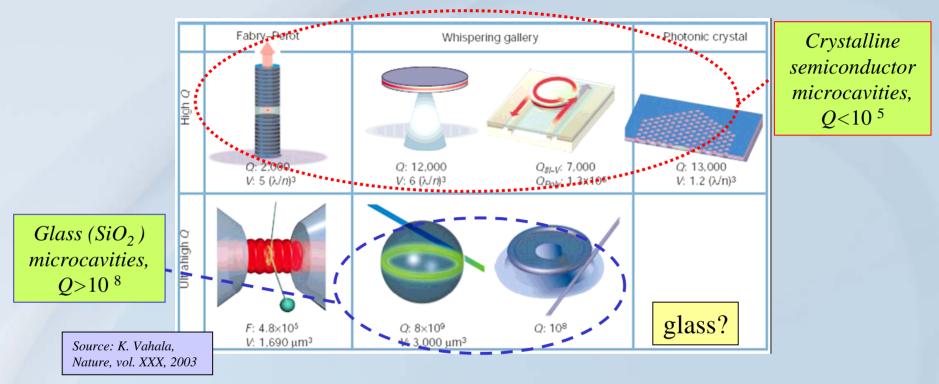

### Microcavities in crystals vs. glasses

ANERSI I

**0 Q** factor of microcavities typically limited by surface scattering loss

⇒ lithography/etching steps used to form semiconductor microstructures

$\Rightarrow$  surface tension can be employed in the manufacture of glass microstructures

### **Glass composites**

• extensive research on nano-composite materials of numerous types:

- $\Rightarrow$  nanocrystal-embedded glasses

- $\Rightarrow$  glass-ceramics

- $\Rightarrow$  hybrid inorganic-organic materials

**2** ex. chalcogenide glass / polymer composites can enable all-solid photonic crystals

$\Rightarrow$  thermo-mechanical compatibility and  $n_2/n_1 \sim 1.8$  or greater

#### Research challenge: glass/polymer microphotonics

<u>A scientific challenge:</u> is it possible (using organic and inorganic glasses) to build chip-scale microphotonics, with diverse functionality, within or above the interconnect layers of silicon chips?

#### Key material requirements:

- **1** <u>Process compatibility</u>

- $\Rightarrow$  must be processible within a back-end 'thermal budget'

- $\Rightarrow$  should not degrade the performance of underlying electronics (by contamination, etc.)

#### **2** <u>chip-scale integrated optics</u>

⇒ must provide high index contrast (approaching that of SOI) to enable micron-scale bends, resonators, and photonic crystal building blocks

⇒ ideally should support 3*d* photonic integration

#### **8** <u>multifunctional photonic circuitry</u>

⇒ integration of passive/active materials is necessary

$\Rightarrow$  ideally, set of materials should enable a full range of active photonic functionality (photo/electroluminescence, electro-optic, Kerr nonlinear, acousto-optic, magneto-optic, thermo-optic, ...)

### Summary of Interests and Contact Information

- integrated optics for fiber networks and computing

- e silicon-based microphotonics

- **3** chalcogenide glasses for photonics

- **4** rare-earth doped glasses for waveguide amplifiers and sources

- **5** nonlinear integrated optics

#### **Contact information**

Ray DeCorby University of Alberta Electrical and Comp. Engineering 7<sup>th</sup> Floor, 9107 – 116 Street N.W. Edmonton, Alberta, Canada, T6G 2V4 *email*: <u>rdecorby@trlabs.ca</u>

### Silicon CMOS – a few facts (1)

• a microprocessor contains an incredibly complex <u>on-chip network of</u> <u>interconnections</u>

> $\Rightarrow$  The Intel 'Montecito' processor (~2007) will contain > 1 billion transistors, clock rate >10 GHz

$\Rightarrow$  chips already contain >7 km of interconnect wires per cm<sup>2</sup>

⇒ up to 9 layers of interconnects used now; >15 layers envisioned

⇒Chip cost is dominated by wires; adding layers is expensive

⇒ microprocessors dissipate several hundred Watts per cm<sup>2</sup>; ~50% is due to resistive losses in interconnect metal

Source: MOTOROLA

### Silicon CMOS – a few facts (2)

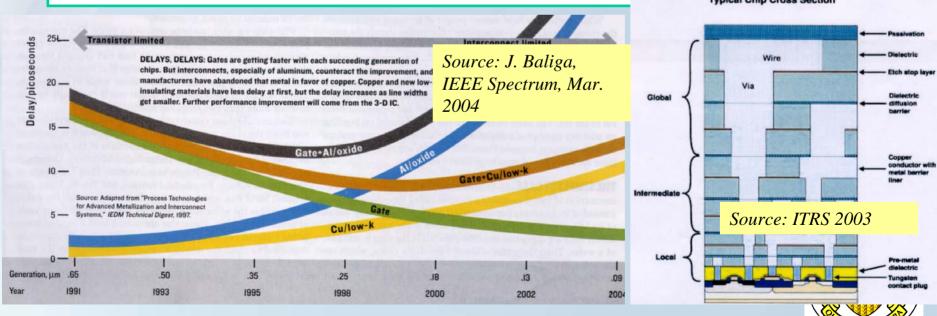

- 2 interconnects pose the greatest challenge to the continuation of Moore's law

- ⇒ wire 'bandwidth' scales downwards with feature size

- ⇒ processors increasingly 'wait around' for data (from memory etc.)

- ⇒Longer 'global' interconnects pose the biggest problem

Copper wires and low k dielectrics developed at great cost to the industry; will provide temporary relief only

⇒ lots of solutions under study; new chip architectures, microwave/wireless solutions, on-chip optical interconnects